La unión híbrida 3D Cu-Cu en la alimentación de los futuros productos de HPC e IA

El encapsulado de semiconductores ha evolucionado desde los tradicionales niveles 1D de las placas de circuito impreso hasta la unión híbrida 3D de última generación a nivel de oblea, logrando pasos de interconexión tan pequeños como un solo micrómetro y un ancho de banda de más de 1.000 GB/s. Los parámetros clave son la potencia, el rendimiento, la superficie y el coste. La eficiencia energética se mejora con técnicas de encapsulado innovadoras, mientras que el rendimiento se beneficia de pasos de interconexión más cortos.

Los requisitos de superficie varían en función de los chips de alto rendimiento y el factor de forma z, más pequeño, de la integración 3D. Las estrategias de reducción de costes pasan por explorar materiales alternativos y mejorar la eficiencia de la fabricación. En el ámbito de la integración 3D, la tecnología de microbombas (microbump) sigue avanzando para lograr pasos más pequeños, con métodos de conexión Cu-Cu innovadores como la unión híbrida a la cabeza, que logra pasos de <1 micra. Este artículo presenta la tecnología híbrida Cu-Cu, incluyendo su desarrollo, la metodología de alto nivel para conseguirla y las aplicaciones clave. Este artículo comparte algunas de las investigaciones del informe de IDTechEx "Advanced Semiconductor Packaging 2024-2034: Forecasts, Technologies, Applications".

Introducción a la tecnología de microbump y unión híbrida

La tecnología de microbump, muy arraigada en el ámbito del encapsulado de semiconductores, se basa en el proceso de unión por compresión térmica (TCB) y tiene una amplia aplicación en diversos productos. Su evolución gira principalmente en torno al escalado continuo del paso de bumping. Sin embargo, surge un obstáculo importante, ya que la reducción del tamaño de las bolas de soldadura conduce a una mayor formación de compuestos intermetálicos (IMC), lo que compromete la conductividad y las propiedades mecánicas. Además, la proximidad de los huecos de contacto puede provocar la formación de puentes entre las bolas de soldadura durante el reflujo, con el consiguiente riesgo de fallo del chip. Dado que la soldadura y los IMC presentan una mayor resistividad que el cobre, su utilización en el encapsulado de componentes de alto rendimiento se enfrenta a limitaciones.

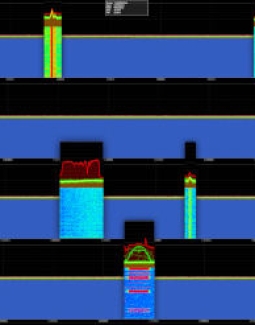

Por otro lado, la unión híbrida presenta un cambio de paradigma al establecer interconexiones mediante una combinación de material dieléctrico (por ejemplo, SiO2 o SiCN) y metal incrustado (Cu). En particular, la unión híbrida Cu-Cu ha logrado pasos inferiores a 10 micrómetros, normalmente en torno a valores de un solo dígito µm. Este avance aporta varias ventajas, como la ampliación de las E/S, el aumento del ancho de banda, la mejora del apilamiento vertical en 3D, el aumento de la eficiencia energética y la reducción de las parásitas y la resistencia térmica gracias a la ausencia de relleno. Sin embargo, esta técnica avanzada sigue planteando dificultades de fabricación y costes elevados.

Tres formas de unión híbrida Cu-Cu

Existen tres métodos principales para lograr la unión híbrida: pastilla (die) a pastilla (D2D), pastilla a oblea (D2W) y oblea a oblea (W2W). Cada método ofrece ventajas e inconvenientes distintos, lo que influye en su idoneidad para diversas aplicaciones.

La unión die to die (D2D) ofrece el mayor rendimiento de ensamblaje, ya que ambas pastillas pueden someterse a pruebas individuales antes de la unión. Este método también ofrece la mayor flexibilidad de diseño. Sin embargo, su rendimiento es muy bajo y presenta importantes dificultades durante el proceso, sobre todo en lo que respecta a los efectos de los bordes, la contaminación y las partículas introducidas durante la singulación. Además, la unión pastilla a pastilla requiere equipos de pick & place con una precisión excepcionalmente alta. Debido a estas dificultades de fabricación y al bajo rendimiento, este método tiene actualmente un uso comercial limitado en aplicaciones de unión híbrida.

La unión de oblea a oblea destaca por su alto rendimiento, que es crucial en la industria de semiconductores. Los pasos del proceso son más sencillos que en el pegado pastilla a pastilla, ya que no es necesario cortar las pastillas ni realizar procedimientos de pick and place. Sin embargo, la unión de oblea a oblea puede reducir el rendimiento y la flexibilidad de diseño, ya que las pastillas superior e inferior deben tener el mismo tamaño. A pesar de estos inconvenientes, la unión de oblea a oblea sigue siendo el método más utilizado para la unión de híbridos Cu-Cu en las aplicaciones comerciales actuales.

La unión pastilla-oblea se sitúa en un punto intermedio entre los métodos pastilla a pastilla y oblea a oblea. Este método ofrece una mayor flexibilidad de diseño y rendimiento que la unión de oblea a oblea. Sin embargo, se enfrenta a retos relacionados con un menor rendimiento y unos requisitos de procesamiento más complejos. A pesar de estas dificultades, la unión pastilla-oblea ha cobrado impulso por su capacidad de lograr un equilibrio entre flexibilidad de diseño y eficiencia de fabricación.

En general, la elección del método de unión híbrida depende de factores como los requisitos de rendimiento del ensamblaje, la flexibilidad del diseño, las consideraciones de rendimiento y los retos de procesamiento. Cada método ofrece distintas ventajas y desventajas, lo que determina su aplicabilidad en el empaquetado y la integración de semiconductores.

Aplicación de la unión híbrida en chips HPC

La adopción más destacada de la unión híbrida es la de AMD, que emplea la tecnología SOIC 3D (unión híbrida) de TSMC para apilar pastillas de caché L3 en un chip informático en dos líneas de productos: la CPU de consumo AMD Ryzen 7000X3D para ordenadores de sobremesa (incl. AMD Ryzen™ 9 7950X3D y AMD Ryzen 7 5800X3D) y el procesador EPYC para informática de alto rendimiento (HPC). AMD destaca el papel de la unión híbrida a la hora de superar sus objetivos de eficiencia energética con la arquitectura habilitada para chiplets y 3D. Destacan su superioridad con respecto a la tecnología de microbump 3D, citando una densidad de interconexión 15 veces mayor y una eficiencia energética 3 veces superior. Otros ejemplos son el Bow Intelligence Processing Unit (BOW) de Graphcore, el primer procesador 3D Wafer-on-Wafer (WoW) del mundo, que utiliza la tecnología de 7 nm de TSMC y la tecnología 3D SoIC de TSMC para una matriz 3D, con 1.472 mosaicos IPU-Core y 900 MB de memoria en el procesador, ofreciendo un rendimiento de IA hasta un 40% más rápido y un 16% más de rendimiento por vatio en comparación con su predecesor 2D. Otro ejemplo clave es la utilización de la unión híbrida en la memoria de gran ancho de banda (HBM). Los principales actores del mercado de HBM, como SK Hynix, Samsung y Micron, están explorando cada vez más la unión híbrida para sus aplicaciones. Aunque el apilamiento de microbombas ha sido el método tradicional de HBM, la creciente demanda de mayor ancho de banda y eficiencia energética está impulsando la investigación activa de la unión híbrida. Se espera que los HBM basados en la unión híbrida se comercialicen en la próxima generación o posteriormente, lo que ofrecerá una ventaja competitiva sustancial sobre las alternativas basadas en microbump. De este modo, estos competidores dispondrán de una gran ventaja frente al actual líder del mercado.

Resumen

La tecnología de unión híbrida está llamada a revolucionar el panorama de los futuros productos de HPC e IA, ya que ofrece una serie de ventajas que darán forma al sector.

Autor: Dr. Yu-Han Chang, analista tecnológico senior de IDTechEx

Articulos Electrónica Relacionados

- El crecimiento de sistemas ele... El informe IC Market Drivers 2018 clasifica las principales aplicaciones de uso final y su impacto en el crecimiento del mercado de CIs. Se pronostica que las v...

- Una forma más rápida de enseña... Imagine que compra un robot para realizar tareas domésticas. Este robot ha sido construido y entrenado en una fábrica para realizar una serie de tareas y nunca ...

- IA y el camino hacia la plena ... El camino hacia los vehículos totalmente autónomos es, por necesidad, largo y sinuoso; los sistemas que implementan nuevas tecnologías que aumentan el nivel de ...

- Previsiones tecnológicas para ... Otro año de crisis por la COVID-19 ha demostrado que el impulso de las soluciones de potencia innovadoras apenas ha disminuido, si bien este avance conlleva sus...

- Un chip de baja potencia y pro... En previsión de la era de la electrónica controlada por voz, los investigadores del MIT han construido un chip de baja potencia especializado para...

- La nanotecnología permitirá de... AIMPLAS participa en el proyecto desarrollando nuevos recubrimientos antihielo basados en nanomateriales que podrán ser incorporados en forma de pinturas...

- Un nuevo método para escalar l... Los materiales 2D tienen un enorme potencial en la miniaturización de componentes electrónicos, y también añaden una gran variedad de posibilidades a las tecnol...

- Almacenamiento de energía medi... Un equipo de investigadores de la Escuela Técnica Superior de Ingeniería y Diseño Industrial (ETSIDI) de la Universidad Politécnica de Madrid (UPM) ha realizado...

- Los ingresos en servicios de i... Un nuevo informe de Juniper Research ha previsto que en el año 2019, el mercado mundial de los servicios basados en el gesto y las tecnologías de interfaz biomé...

- Potencial de los sensores piez... Los sensores de presión impresos son una tecnología consolidada, que se ha utilizado en aplicaciones como los sensores de ocupación de automóviles, los pianos e...

- La visión artificial acelera l... La detección de imágenes es una capacidad esencial, utilizada en múltiples aplicaciones que van desde las cámaras web y las cámaras de los smartphones hasta los...

- Solución de reciclaje para la ... El sector de la aviación se encuentra en un período de transformación hacia una movilidad más sostenible, eficiente y segura. La industria está en constante cam...